Научная электронная библиотека

Монографии, изданные в издательстве Российской Академии Естествознания

1.4 Синтез функциональных подсхем микросхем управления на основе принципа схемотехнической интеграции

Современные микросхемы имеют в своем составе широкий набор различных функциональных узлов. Их реализация в виде отдельных функциональных подсхем, как правило, приводит к недопустимому увеличению числа элементов схемы, что связано со снижением надежности таких схем и их высокому токопотреблению. Применение принципа схемотехнической интеграции позволяет избежать перечисленных недостатков, к тому же схемы, проектируемые на основе этого принципа, отличаются своей простотой и изяществом.

.

.

Его сущность заключается в том, что ряд отдельных функциональных узлов выполняется в виде единой нерасчленимой подсхемы, объединяющей совокупность функций всех изначальных узлов.

Рассмотрим особенности данного принципа на примерах схемотехнического построения элементов ФСОС и УЗСР. На рис.1.14 элемент ФСОС реализован на основе неинвертирующего усилителя (VT1-VT11,R1,R2,R5,I1), инвертирующего решающего усилителя (VT12-VT20,12-14,R3.R4) и ограничителя (VT21-VT23.I5). Данный ФСОС реализует зависимость Uос=f(Uр) (рис.1.10). На участке от нуля до величины U2 инвертирующий и неинвертирующий усилители находятся в режиме ограничения. На участке U2 –U3 инвертирующий усилитель находится в линейном режиме, а неинвертирующий - в режиме ограничения. На участке U3 -Uк, оба усилителя работают в линейном режиме. При напряжении Up, превышающем значение Uк, инвертирующий, а затем и неинвертирующий усилители перейдут в режим ограничения. Данная схемная реализация инвертирующего и неинвертирующего усилителей позволяют им функционировать при уровне синфазного напряжения близком к нулю.

Коэффициенты усиления инвертирующего и неинвертирующего усилителей определяются следующими соотношениями:

, (1.34)

, (1.34)

где R3 =R1 =R2; S1 - площадь эмиттерного перехода i-го транзистора. Значения напряжений Ux„ и Uz можно найти из выражений:

Ux = U0 - I1KNR6, Uz = U3 - I1Rэ (1.35)

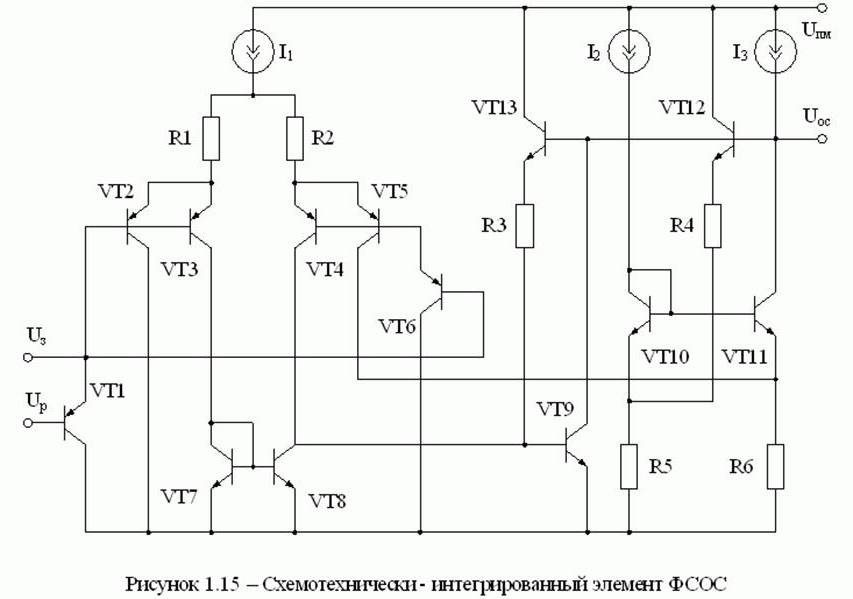

Элемент ФСОС, реализованный на основе принципа схемотехнической интеграции, представлен на рис.1.15. В данной подсхеме инвертирующий, неинвертирующий усилители и ограничитель выполнены в виде единого неразделимого схемного блока, реализующего зависимость Uос= f(Uр) (рис.1.10). Коэффициенты передачи для участков Uz –U3 и U3 -Uк при условии I2 = I3, R5 = R5, R1 = R2 определяются соотношениями:

.

.

. (1.36)

. (1.36)

Значения напряжений Uz, Ux и U0 определяются соотношениями:

. (1.37)

. (1.37)

Из рассмотрения схемотехнических решений элемента ФСОС (рис.1.14, 1.15) следует, что применение принципа схемотехнической интеграции позволило более чем в 2 раза сократить количество активных элементов, а так же снизить суммарный потребляемый ток.

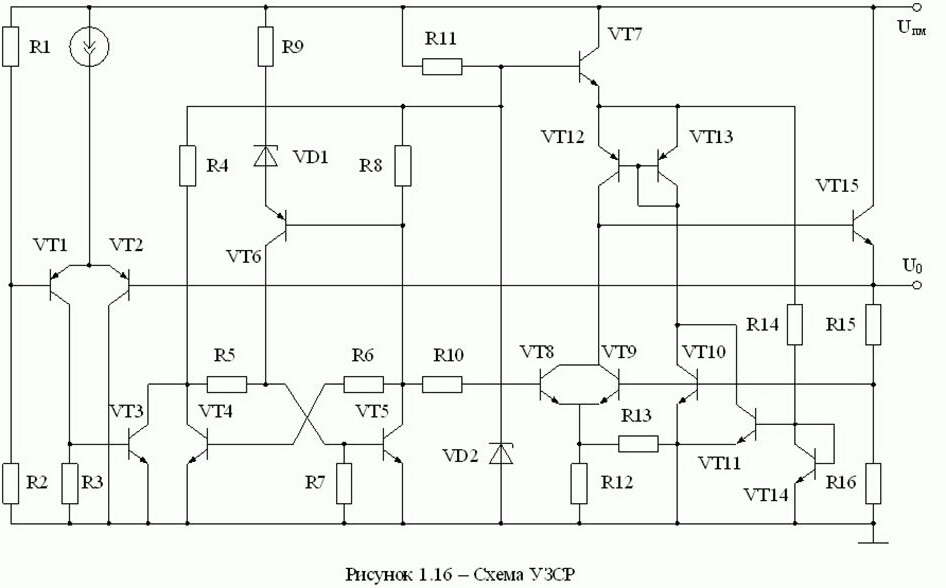

На рис.1.16 представлена схемотехническая реализация элемента. Он включает в себя: переключатель тока (I1, VT1, VT2, R1, R2), триггер (VT3-VT5, R3-R8), формирователь гистерезиса (VT6, VD1, R9), ключ (VT8, R10), параметрический стабилизатор (VT7, VD2, R11), компенсационный стабилизатор (VT9, VT10, VT12, VT13, VT15, R12, R13, R15, R16) и цепь запуска (VT11, VT14, R14).

Данная схема реализует зависимость U0 =f(Uпм), необходимую для реализации режима запуска (рис.1.11). При подаче напряжения Uпм.триггер устанавливается в состояние, при котором ключ замкнут, а выходное напряжение компенсационного стабилизатора близко к нулю. При достижении напряжением Uпм величины Uпм2 триггер переключается в состояние, соответствующее разомкнутому положению ключа, при этом выходное напряжение равно величине U0. Обратное выключение происходит при меньшем напряжении Uпм (Uпм1) из-за изменения порога срабатывания переключателя тока.

Величина выходного напряжения U0 определяется выражением:

, (1.38)

, (1.38)

где φт≈25 мВ - температурный потенциал, Uэбi - напряжение эмиттер-база i-го транзистора. Напряжения включения и выключения соответствуют

.

.

.

.

выражениям:

(1.39)

(1.39)

где UVD1- напряжение стабилизации элемента VD1.

.

.

В схемотехническом варианте реализации элемента УЗСР (рис.1.17.а) переключатель тока, формирователь гистерезиса и триггер объединены в единой подсхеме (V1-VT11, R1-R4). При увеличении напряжения Uпм, выходное напряжение компенсационного стабилизатора (VT12-VT18, R5-R8) появляется, когда токи коллекторов транзисторов VT2 и VT4 равны величине Iр (рис.1.17.6). Величины напряжений включения и выключения, соответствующие зависимости U0 =f(Uпм) (рис.1.11) определяются выражениями:

. (1.40)

. (1.40)

Величину тока Iр можно найти из соотношения:

Ip=2φтln(S4/S3)/R2. (1.41)

Таким образом, разработанные схемотехнические решения показывают, что использование принципа схемотехнической интеграции на этапе синтеза функциональных подсхем позволяет снизить число элементов схемы и повысить к.п.д. устройства в целом.